## Серия 5575BB радиационно-стойких микросхем гальванической развязки, разработанных в рамках ОКР «Интерфейс-ИЗ-Т»

## Назначение

Серия радиационно-стойких микросхем гальванической развязки предназначена для передачи информационных сигналов между двумя независимыми электрическими цепями.

## Основные характеристики:

- напряжение питания 2,7 ÷ 3,63 В;

- ток потребления не более 15 мА на канал (при U<sub>CC</sub>=3,3 В и частоте 10 МГц);

- скорость передачи до 150 Мбит/сек;

- температурный диапазон от минус 60°C до 85°C;

- тип входных сигналов КМОП/TTL, LVDS/LVDM;

- тип выходных сигналов КМОП, LVDS/LVDM;

- холодный резерв по всем входам и выходам LVDS/LVDM интерфейсов;

- повышенная радиационная стойкость к факторам космического пространства;

- микросхемы изготовлены по радиационно-стойкой КМОП-технологии на структурах «кремний на изоляторе» с топологическими нормами 0.25мкм;

- напряжение изоляции не менее 2000 В;

- задержка распространения сигнала не более 5нс.

## Краткое описание

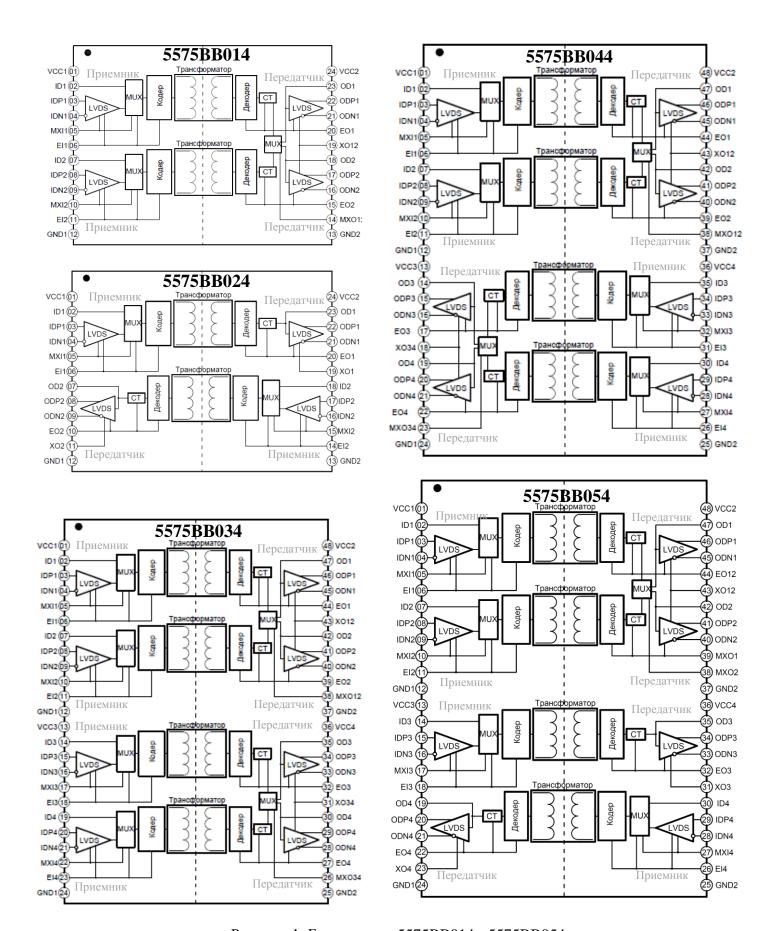

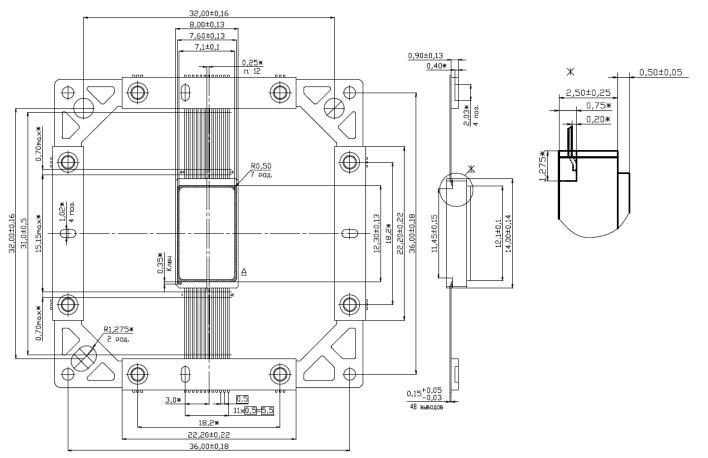

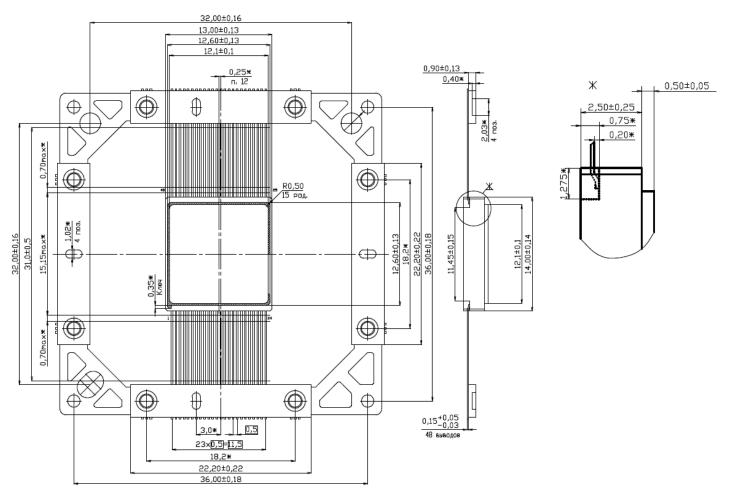

Серия микросхем гальванической развязки 5575 включает в свой состав пять типов микросхем (таблица 1). Микросхемы обеспечивают передачу информации по двум или четырем независимым каналам. Структурные схемы микросхем 5575ВВ014 - 5575ВВ054 представлены на рисунке 1. В каждом канале передатчик и приемник изолированы друг от друга с помощью трансформатора. Чертежи корпусов представлены на рисунке 2.

В приемнике имеется возможность выбора работы с одним из двух типов входных информационных сигналов: в соответствии с LVDS интерфейсом или КМОП/ТТL (таблица 2). В режиме LVDS/LVDM интерфейса входные сигналы подаются на выводы IDPi и IDNi. В режиме КМОП/ТТL сигнала - на вывод IDi. Выбор типа входного сигнала осуществляется управляющим сигналом MXIi. При низком уровне на MXIi осуществляется прием сигнала на входе IDi, при этом LVDS приемник отключатся, а входы IDPi и IDNi доопределяются до низкого уровня. При высоком уровне на MXIi осуществляется прием сигналов на IDPi и IDNi LVDS приемника, а вход IDi доопределяется до низкого уровня.

В приемнике имеется схема обновления уровня сигнала обеспечивающая прием информации о состоянии уровня входного сигнала не реже, чем раз в n мкс, тогда как схема контроля сигнала в передатчике устанавливает низкий уровень на выходах ODi и ODPi и ODNi если информация о состоянии сигнала не обновлялась в течении 4\*n мкс. Схема обновления уровня сигнала функционирует от внутренних тактовых генераторов и не отключаются при блокировании передатчика или приемника.

Выходной сигнал передатчика подается одновременно на LVDS/LVDM интерфейс - выходы ODPi и ODNi и КМОП цифровой выход ODi. При низком уровне на входе XOj устанавливается максимальный выходной ток на ODi не более 4 мA и LVDS интерфейс на ODPi и ODNi. При высоком уровне на входе XOj устанавливается максимальный выходной ток на ODi не более 12 мA и LVDM интерфейс на ODPi и ODNi (таблица 3).

В 5575ВВ014, 5575ВВ034 - 5575ВВ054 имеется функция мультиплексирования выходных данных между каналами при помощи управляющего входа МХО*i*. При низком уровне на МХО*i*

осуществляется прямая передача информации между каналами, при высоком уровне на MXO*i* происходит переключение на соседний канал (таблица 4).

Перевод приемника в состояние «Выключено» осуществляется низким уровнем на управляющем входе EIi, при этом LVDS приемник отключается, входы IDPi, IDNi и IDi доопределяются до низкого уровня.

Перевод передатчика в состояние «Выключено» осуществляется низким уровнем на управляющем входе EOi, при этом LVDS/LVDM выходы переводятся в высокоимпедансное состояние,  $KMO\Pi$  – в низкий уровень.

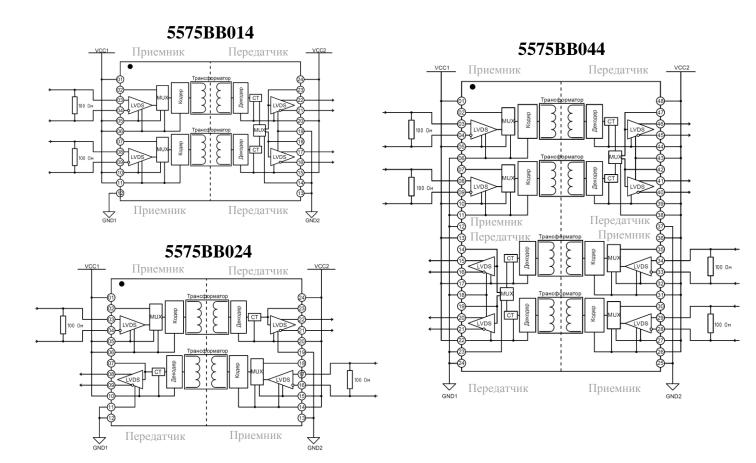

На рисунке2 представлены рекомендуемые схемы включения 5575BB014 - 5575BB054 в режиме LVDS.

Таблица 1 Состав серии.

| Тип       | Количество каналов, шт. | Направление передачи     | Количество выводов |

|-----------|-------------------------|--------------------------|--------------------|

| 5575BB014 | 2                       | 2 в прямом               | 24                 |

| 5575BB024 | 2                       | 1 в прямом, 1 в обратном | 24                 |

| 5575BB034 | 4                       | 4 в прямом               | 48                 |

| 5575BB044 | 4                       | 2 в прямом, 2 в обратном | 48                 |

| 5575BB054 | 4                       | 3 в прямом, 1 в обратном | 48                 |

Таблица 2 Режимы работы приемника.

| EIj | MXIj    | IDPj/IDNj                           | IDj                                                      |

|-----|---------|-------------------------------------|----------------------------------------------------------|

|     |         | Включен резистор доопределения      | Включен резистор доопределения                           |

| 0   | 0 или 1 | 255 кОм до низкого уровня           | 100 кОм до низкого уровня                                |

|     |         | (LVDS приемник в режиме пониженного | (приемник отключен)                                      |

| 1   | 0       | энергопотребления)                  | Прием сигнала КМОП/ТТЛ уровня                            |

| 1   | 1       | Прием сигнала по LVDS интерфейсу    | Включен резистор доопределения 100 кОм до низкого уровня |

Таблица 3 Управление мощностью выходных сигналов.

| XO12 | ODPi/ODNi                      | $\mathrm{OD}i$                |

|------|--------------------------------|-------------------------------|

| 0    | LVDS (I <sub>OLH</sub> =3,5mA) | KMOП ( $I_{OLH}$ =4 $MA$ )    |

| 1    | LVDM (I <sub>OLH</sub> =7,0mA) | КМОП (I <sub>OLH</sub> =12мА) |

Таблица 4 Управление направлением передачи.

| Управляющие входы |     | ие входы | Выходы                         |                                |

|-------------------|-----|----------|--------------------------------|--------------------------------|

| EO1               | EO2 | MXO12    | ODP1/ODN1, OD1                 | ODP2/ODN2, OD2                 |

| 1                 |     | 0        | Передача данных из приемника 1 | Передача данных из приемника 2 |

|                   | 1   | 1        | Передача данных из приемника 2 | Передача данных из приемника 1 |

| 0                 | 1   | 0        | Отключен*                      | Передача данных из приемника 2 |

|                   |     | 1        | Передача данных из приемника 2 | Отключен*                      |

| 1                 | 0   | 0        | Передача данных из приемника 1 | Отключен*                      |

|                   |     | 1        | Отключен*                      | Передача данных из приемника 1 |

| 0                 | 0   | 0,1      | Отключен*                      | Отключен*                      |

<sup>\*-</sup> при этом LVDS/LVDM выходы переводятся в высокоимпедансное состояние, КМОП выходы в низкий уровень.

Рисунок 1. Блок- схемы 5575ВВ014 - 5575ВВ054

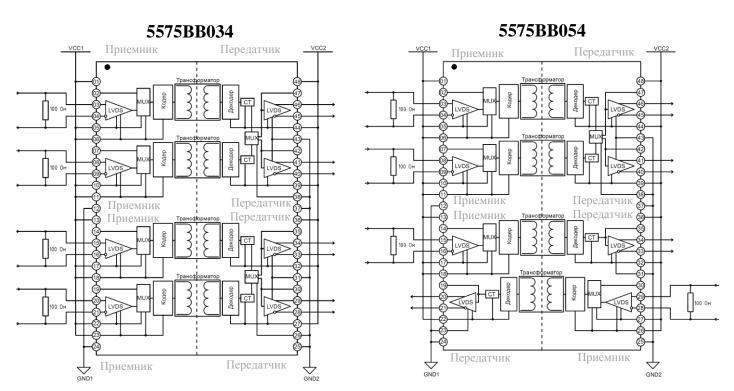

Рисунок 2. Рекомендуемые схемы включения 5575BB014 - 5575BB054 в режиме LVDS

Рисунок 2. Чертеж корпуса микросхем 5575ВВ014 и 5575ВВ024

Рисунок 3. Чертеж корпуса микросхем 5575ВВ034 - 5575ВВ054